# AN6591FJM

Transmission / reception, single chip PLL IC for PHS, cordless telephone

# Overview

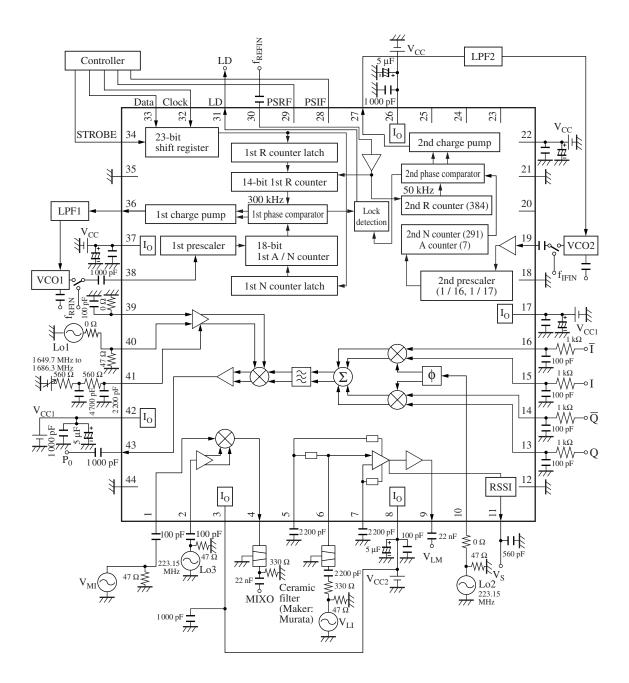

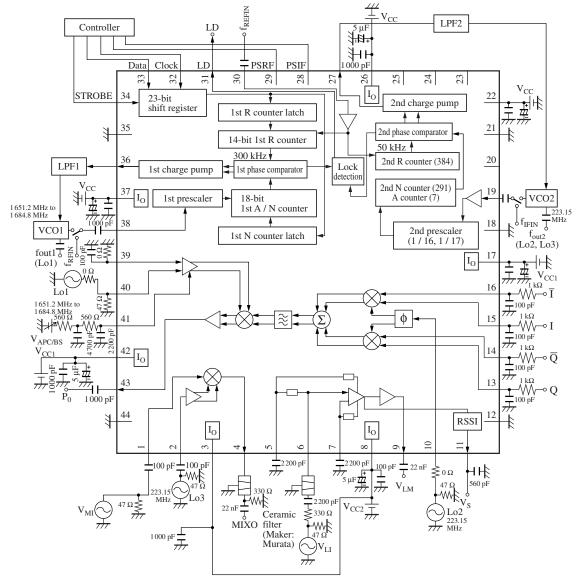

AN6591FJM is a single chip IC optimum for PHS, and a quadrature modulator, reception IF and PLL are integrated in it.

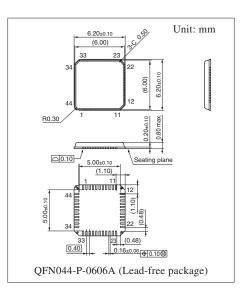

As this IC is housed in a QFN package (quad flat nonleaded PKG), realization of compact equipment through this super-small package is possible.

## Features

- Transmission and reception PLL block on a single chip

- Transmission block: A quadrature modulator, a phase shifter APC (auto power control) and an up-converter

- Reception block: A down-mixer (to 300 MHz), an IF amplifier and an RSSI circuit

- PLL block: PLLs for 1st and 2nd local oscillators.

- 6 mm × 6 mm small package

#### Applications

• PHS, digital cordless telephone, etc.

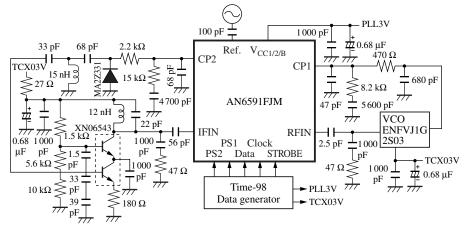

# Application Circuit Example

#### Pin Descriptions

| Pin No. | Symbol           | Description                 | Pin No. | Symbol           | Description              |

|---------|------------------|-----------------------------|---------|------------------|--------------------------|

| 1       | RXMXIN           | RX mix. in                  | 23      | N.C.             |                          |

| 2       | RXLOIN           | RX local in                 | 24      | N.C.             |                          |

| 3       | V <sub>CC2</sub> | V <sub>CC</sub> mix.        | 25      | N.C.             |                          |

| 4       | MXO              | Mix. out                    | 26      | V <sub>CC</sub>  | V <sub>CC</sub> 2nd CMOS |

| 5       | LMDEC1           | Lim. decouple1              | 27      | CP2              | 2nd charge pump out      |

| 6       | LMIN             | Lim. in                     | 28      | PSIF             | 2nd power save in        |

| 7       | LMDEC2           | Lim. decouple2              | 29      | PSRF             | 1st power save in        |

| 8       | V <sub>CC2</sub> | V <sub>CC</sub> lim.        | 30      | Ref.             | Reference in             |

| 9       | LMO              | Lim. out                    | 31      | LD               | Lock detect out          |

| 10      | TXLO2            | TX local2 in                | 32      | Clock            | Clock in                 |

| 11      | RSO              | RSSI out                    | 33      | Data             | Serial data in           |

| 12      | GND              | GND                         | 34      | STROBE           | Strobe in                |

| 13      | Q-in             | Q-input                     | 35      | GND              | GND 1st / 2nd CMOS       |

| 14      | Q-in             | Q-input                     | 36      | CP1              | 1st charge pump out      |

| 15      | I-in             | I-input                     | 37      | V <sub>CC</sub>  | V <sub>CC</sub> 1st CMOS |

| 16      | Ī-in             | Ī-input                     | 38      | RFIN             | 1st prescaler in         |

| 17      | V <sub>CC1</sub> | V <sub>CC</sub> TX mod.     | 39      | TXLO1            | TX local 1               |

| 18      | GNDM             | GND TX mod.                 | 40      | TXLO1R           | TX local 1ref.           |

| 19      | IFIN             | 2nd prescaler in            | 41      | APC / BS         | APC / BS                 |

| 20      | N.C.             |                             | 42      | V <sub>CC1</sub> | V <sub>CC</sub> TX out   |

| 21      | GND2             | GND 2nd CMOS                | 43      | TXO              | TX output                |

| 22      | V <sub>CC</sub>  | V <sub>CC</sub> 1st 2nd BIP | 44      | GNDO             | GND TX out               |

### Absolute Maximum Ratings

| Parameter                        | Symbol           | Rating      | Unit |

|----------------------------------|------------------|-------------|------|

| Supply voltage                   | V <sub>CC</sub>  | 3.5         | V    |

|                                  | V <sub>CC1</sub> |             |      |

|                                  | V <sub>CC2</sub> |             |      |

| Supply current *2                | I <sub>CC</sub>  | 54          | mA   |

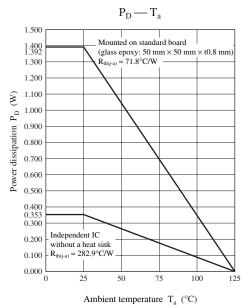

| Power dissipation *2             | P <sub>D</sub>   | 194         | mW   |

| Operating ambient temperature *1 | T <sub>opr</sub> | -20 to +70  | °C   |

| Storage temperature *1           | T <sub>stg</sub> | -55 to +125 | °C   |

Note) \*1: Except for the operating ambient temperature and storage temperature, all ratings are for  $T_a = 25^{\circ}C$ .

\*2: The above power dissipation  $P_D$  shows the power dissipation of the package without heat sink. Refer to "**Technical Data**" when mounting this IC to a PCB and check that the IC will operate within the package power dissipation range.

#### Recommended Operating Range

| Parameter      | Symbol                                                      | Range      | Unit |

|----------------|-------------------------------------------------------------|------------|------|

| Supply voltage | $\begin{vmatrix} V_{CC}, V_{CC1}, \\ V_{CC2} \end{vmatrix}$ | 2.7 to 3.3 | V    |

#### Electrical Characteristics at T<sub>a</sub> = 25°C

| Parameter                                  | Symbol             | Test<br>circuit | Conditions                                                                                                                                                                                                                                             | Min  | Тур  | Max  | Unit    |

|--------------------------------------------|--------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---------|

| Current consumption (reception)            | I <sub>CCRX</sub>  | 2               | No signal input                                                                                                                                                                                                                                        | _    | 5.3  | 6.8  | mA      |

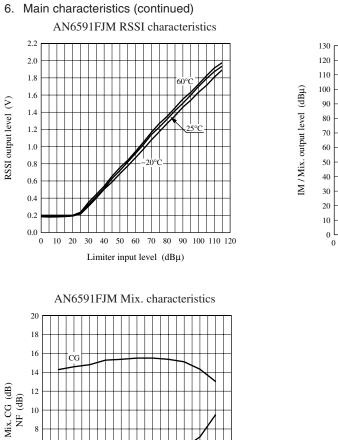

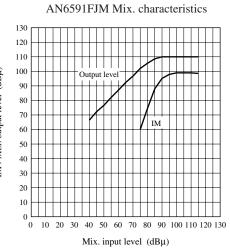

| Mix. conversion gain                       | G <sub>MX</sub>    | 1               | $V_{\rm MI}$ = 70 dBµ Filter loss excluded.                                                                                                                                                                                                            | 13   | 16   | 19   | dB      |

| Mix. max. output level                     | V <sub>MX</sub>    | 1               | $V_{MI} = 105 \text{ dB}\mu$ Filter loss excluded.                                                                                                                                                                                                     | 105  | 110  |      | dBµ     |

| Lim. voltage gain                          | G <sub>LM</sub>    | 1               | $V_{MI} = 20 \text{ dB}\mu$                                                                                                                                                                                                                            | 63   | 68   | 73   | dB      |

| Lim. max. output amplitude                 | V <sub>LM</sub>    | 1               | $V_{LI} = 80 \text{ dB}\mu$                                                                                                                                                                                                                            | 350  | 400  | _    | mV[p-p] |

| RSSI output voltage (1)                    | $V_{S}(1)$         | 1               | V <sub>LI</sub> : No signal input                                                                                                                                                                                                                      | 0    | 0.2  | 0.5  | V       |

| RSSI output voltage (2)                    | V <sub>S</sub> (2) | 1               | $V_{LI} = 115 \text{ dB}\mu$                                                                                                                                                                                                                           | 1.60 | 1.80 | _    | V       |

| Change in RSSI output                      | D <sub>S</sub>     | 1               | $\begin{split} V_{S} \left( V_{IS} \right) &= V_{S}(1) + 0.15 \ V \\ D_{S} \left( 1 \right) &= V_{S} \left( V_{IS} + 65 \ dB\mu \right) - V_{S} \left( V_{IS} \right) \end{split}$                                                                     | 1.0  | 1.25 | 1.5  | V       |

| Gradient of RSSI output                    | $\Delta D_{S(n)}$  | 1               | $\begin{split} \Delta D_{S} \left( n \right) &= 5 \left( V_{S} \left( V_{IS} + n13 \; dB\mu \right) - \right. \\ V_{S} \left( V_{IS} + \left( n-1 \right) \; 13 \; dB\mu \right) \right) / \; D_{S} \left( 1 \right) \\ n &= 1 \; to \; 5 \end{split}$ | 0.75 | 1.0  | 1.25 | _       |

| Current consumption<br>(transmission)      | I <sub>CCTX</sub>  | 1               | Lo1 = 233.15 MHz, -10 dBm<br>Lo2 = 1672.5 MHz, -10 dBm<br>V <sub>APC</sub> = 2.75 V                                                                                                                                                                    | _    | 28   | 37   | mA      |

| Sleep current in transmission              | ISL                | 2               | No signal input, $V_{APC} = 0 V$                                                                                                                                                                                                                       |      | 0    | 10   | μA      |

| Transmission output level 1 *              | P01                | 1               | Lo1 = 233.15  MHz, -10  dBm<br>$Lo2 = 1660 \text{ MHz}, -10 \text{ dBm}, \text{V}_{APC} = 2.2 \text{ V}$                                                                                                                                               | -13  | -9   |      | dBm     |

| Transmission output level 2 *              | P02                | 1               | Lo1 = 233.15 MHz, -10 dBm<br>Lo2 = 1687 MHz, -10 dBm, V <sub>APC</sub> = 2.2 V                                                                                                                                                                         | -13  | -9   |      | dBm     |

| Image leakage suppression                  | IL1                | 1               | Lo1 = 233.15 MHz, $-10 \text{ dBm}$<br>Lo2 = 1672.5 MHz, $-10 \text{ dBm}$<br>$V_{APC}$ = 2.75 V, I / Q: No level adjusted                                                                                                                             |      | -35  | -30  | dBc     |

| $f_{LO1} + f_{LO2}$<br>leakage suppression | CL                 | 1               | Lo1 = 233.15 MHz, -10 dBm<br>Lo2 = 1672.5 MHz, -10 dBm<br>V <sub>APC</sub> = 2.75 V, I/Q: DC offset adjusted                                                                                                                                           |      | -35  | -30  | dBc     |

| Proximity spurious<br>suppression          | DU                 | 1               | Lo1 = 233.15 MHz, $-10 \text{ dBm}$<br>Lo2 = 1672.5 MHz, $-10 \text{ dBm}$<br>Make V <sub>APC</sub> adjustments so that<br>the Po value will be $-13 \text{ dBm}$ .                                                                                    |      | -55  | -51  | dBc     |

Note) 1. Unless otherwise specified, at reception:  $V_{CC2} = 3.0 \text{ V}$ ,  $V_{LO3} = -10 \text{ dBm}$ , f = 233.15 MHz,  $V_{MI}$ : f = 243.95 MHz, SW1 = a,  $V_{LI}$ : f = 10.8 MHz (The input level of pin 6, except the signal attenuation at the matching circuit and filter circuit.) The  $V_{MO}$  and  $V_{LO}$  values are at high impedance. ( $V_{LM}$  shall be measured at probe load conditions of 27 pF and 1 M $\Omega$ .)

The V<sub>IS</sub> is the input level V<sub>LI</sub> where the RSSI output voltage is V<sub>S</sub> (1) + 0.15 V. At transmission: V<sub>CC1</sub> = 3.0 V, I / Q signal amplitude: 0.5 V[p-p] in both phases, DC bias: 1.5 V, SW1: a

$I_{CCTX}$  , IL1, CL:  $\pi$  / 4 QPSK-modulated wave, P01, P02, DU: PN9-level-modulated wave

I / Q signal input condition: Make an amplitude adjustment of  $\pi$  / 4 QPSK modulation signal 0000 to 0.5 V[p-p] with an oscilloscope and change the signal wave to a PN9-level continuous wave.

Spectrum analyzer setting conditions for transmission output level measurement: SPAN = 2 MHz, RBW = 3 MHz, VBW = 3 MHz, SWPT = 5 s Det.: Pose. peak

\*: P01 output frequency: 1893.15 MHz, P02 output frequency: 1920.15 MHz

# Electrical Characteristics at $T_a = 25^{\circ}C$ (continued)

| Parameter                    | Symbol             | Test<br>circuit | Conditions                                                        | Min | Тур | Max | Unit   |

|------------------------------|--------------------|-----------------|-------------------------------------------------------------------|-----|-----|-----|--------|

| Current consumption 1 (PLL)  | I <sub>CC1</sub>   | 1               | 1st PLL and 2nd PLL blocks are simultaneously turned on.          | 3.7 | 5.4 | 7.0 | mA     |

| Current consumption 2 (PLL)  | I <sub>CC2</sub>   | 1               | 1st PLL block is turned on while the 2nd PLL block is turned off. | 3.0 | 4.4 | 5.7 | mA     |

| Current consumption 3 (PLL)  | I <sub>CC3</sub>   | 1               | 1st PLL block is turned off while the 2nd PLL block is turned on. | 1.2 | 1.7 | 2.2 | mA     |

| Current consumption 4 (PLL)  | I <sub>CC4</sub>   | 1               | Power save mode                                                   |     | 0   | 10  | μΑ     |

| 1st RF input level           | V <sub>RFIN</sub>  | 1               | $f_{RFIN}$ = 1500 MHz to 1800 MHz                                 | -15 |     | -2  | dBm    |

| 2nd IF input level           | V <sub>IFIN</sub>  | 1               | $f_{IFIN}$ = 120 MHz to 300 MHz                                   | -10 | _   | +6  | dBm    |

| Reference signal input level | V <sub>REFIN</sub> | 1               | $f_{REFIN} = 10 \text{ MHz}$ to 25 MHz                            | 0.2 |     | 1.2 | V[p-p] |

Note) Unless otherwise specified,  $V_{CC}$  is 3.0 V and reference signal input level  $V_{REFIN}$  is 0.6 V[p-p] at  $f_{REFIN} = 19.2$  MHz.

#### • Design reference data

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                                                           | Symbol | Test<br>circuit | Conditions                                                                                      | Min | Тур | Max | Unit   |

|---------------------------------------------------------------------|--------|-----------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|--------|

| 1st local leakage suppression                                       | CL1    | 1               | Lo1 = 233.15 MHz, -10 dBm<br>Lo2 = 1672.5 MHz, -10 dBm<br>V <sub>APC</sub> = 2.75 V             |     | -25 | -20 | dBc    |

| 2nd local leakage suppression                                       | CL2    | 1               | Lo1 = 233.15 MHz, -10 dBm<br>Lo2 = 1672.5 MHz, -10 dBm<br>V <sub>APC</sub> = 2.75 V             |     | -15 | -10 | dBc    |

| In-band output level deviation                                      | ΔP     | 1               | Lo1 = 233.15 MHz, -10 dBm<br>Lo2 = 1 660 MHz to 1 687 MHz,<br>-10 dBm, V <sub>APC</sub> = 2.2 V |     |     | 1.0 | dB     |

| Adjacent channel leakage<br>power suppression<br>(600 kHz detuning) | BL1    | 1               | Lo1 = 233.15 MHz, -10 dBm<br>Lo2 = 1672.5 MHz, -10 dBm<br>V <sub>APC</sub> = 2.75 V             |     | -60 |     | dBc    |

| Modulation accuracy                                                 | EVM    | 1               | Lo1 = 233.15 MHz, -10 dBm<br>Lo2 = 1672.5 MHz, -10 dBm<br>V <sub>APC</sub> = 2.2 V              |     | 3   | 5   | %[rms] |

| Min. output level                                                   | Pmin   | 1               | Lo1 = 233.15 MHz, -10 dBm<br>Lo2 = 1672.5 MHz, -10 dBm<br>V <sub>APC</sub> = 1.0 V              |     | -30 | -25 | dBm    |

| RF + 233.15 MHz<br>leakage suppression                              | IIL    | 1               | Lo1 = 233.15 MHz, -10 dBm<br>Lo2 = 1672.5 MHz, -10 dBm<br>V <sub>APC</sub> = 2.75 V             |     | -36 |     | dBc    |

| Mixer output resistance                                             | Rmix   | 2               | No signal input                                                                                 | —   | 330 | —   | Ω      |

Note) Unless otherwise specified,  $V_{CC} = V_{CC1} = V_{CC2} = 3.0 \text{ V}$

I / Q signal: 0.5 V[p-p] in both phases, DC bias: 1.5 V

CL1, CL2,  $|\Delta P|$ , BL1, EVM, Pmin, IIL : PN9-level modulated wave.

- $\blacksquare$  Electrical Characteristics at T<sub>a</sub> = 25°C (continued)

- Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                                       | Symbol               | Test<br>circuit | Conditions                                                                                                                 | Min    | Тур   | Max    | Unit        |

|-------------------------------------------------|----------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|-------------|

| High-level input voltage                        | V <sub>IH</sub>      | 2               |                                                                                                                            | 2.4    |       | —      | V           |

| Low-level input voltage                         | V <sub>IL</sub>      | 2               |                                                                                                                            |        |       | 0.6    | V           |

| High-level output voltage                       | V <sub>OH</sub>      | 2               |                                                                                                                            | 2.4    |       |        | V           |

| Low-level output voltage                        | V <sub>OL</sub>      | 2               |                                                                                                                            |        | _     | 0.6    | V           |

| High-level input current 1                      | I <sub>IH1</sub>     | 2               | V <sub>IH</sub> of 3.0 V applied                                                                                           | _      | 0     | 10     | μΑ          |

| Low-level input current 1                       | I <sub>IL1</sub>     | 2               | V <sub>IL</sub> of 0 V applied                                                                                             | _      | 0     | 10     | μΑ          |

| High-level input current 2                      | I <sub>IH2</sub>     | 2               | V <sub>IH</sub> of 3.0 V applied                                                                                           |        | 0     | 10     | μΑ          |

| Low-level input current 2                       | I <sub>IL2</sub>     | 2               | V <sub>IL</sub> of 0 V applied                                                                                             |        | 0     | 10     | μΑ          |

| High-level output current<br>1 / 2 (High power) | I <sub>OH1H,2H</sub> | 2               | High power with $V_{OH}$ of 2.4 V applied.                                                                                 | -3.2   | -2.6  | -1.9   | mA          |

| Low-level output current<br>1 / 2 (High power)  | I <sub>OL1H,2H</sub> | 2               | High power with $V_{OL}$ of 0.6 V applied.                                                                                 | 2.8    | 3.5   | 4.4    | mA          |

| High-level output current<br>1 / 2 (Low power)  | I <sub>OH1L,2L</sub> | 2               | Low power with $V_{OH}$ of 2.4 V applied.                                                                                  | - 0.74 | - 0.6 | - 0.46 | mA          |

| Low-level output current<br>1 / 2 (Low power)   | I <sub>OL1L,2L</sub> | 2               | Low power with $V_{\rm OL}$ of 0.6 V applied.                                                                              | 0.53   | 0.7   | 0.87   | mA          |

| Output leakage current                          | I <sub>OZ</sub>      | 2               | V <sub>OZ</sub> of 0 V / 3.0 V applied                                                                                     | -1     | 0     | 1      | μΑ          |

| High-level output current 3                     | I <sub>OH3L</sub>    | 2               | V <sub>OH</sub> of 2.4 V applied                                                                                           | -3.6   | -2.6  | -1.5   | mA          |

| Low-level output current 3                      | I <sub>OL3L</sub>    | 2               | V <sub>OL</sub> of 0.6 V applied                                                                                           | 1.9    | 3.3   | 4.6    | mA          |

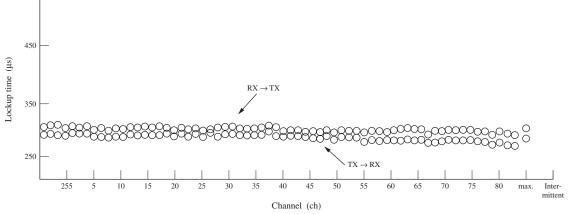

| Lockup time (1st)                               | rockt1               | 1               | 1st PLL block and 2nd PLL block are<br>simultaneously turned on for all chan-<br>nels with RX-to-TX and TX-to-RX<br>burst. |        |       | 600    | μs          |

| Lockup time (2nd)                               | rockt2               | 1               | 1st PLL block and 2nd PLL block are<br>simultaneously turned on intermit-<br>tently (during PS triggering)                 |        |       | 600    | μs          |

| 1st spurious ±50 kHz                            | Lspu1                | 1               | 1st PLL block and 2nd PLL block are<br>simultaneously turned on.<br>L-channel to H-channel                                 |        |       | -40    | dBc         |

| 1st proximity C / N                             | Lspu2                | 1               | 1st PLL block and 2nd PLL block are<br>simultaneously turned on.<br>df = 1 kHz, L-channel to H-channel                     |        |       | -70    | dBc /<br>Hz |

| 1st reference leakage                           | Lspu3                | 1               | 1st PLL block and 2nd PLL block are<br>simultaneously turned on.<br>df = 600 kHz, BW192 kHz                                | —      |       | -67    | dBc         |

Note) Unless otherwise specified,  $V_{CC}$  is 3.0 V and reference signal input level  $V_{REFIN}$  is 0.6 V[p-p] at  $f_{REFIN}$  of 19.2 MHz.

- Electrical Characteristics at T<sub>a</sub> = 25°C (continued)

- Design reference data (continued)

Note) The characteristics listed below are theoretical values based on the IC design and are not guaranteed.

| Parameter                        | Symbol | Test<br>circuit | Conditions                                                                             | Min | Тур | Max | Unit        |

|----------------------------------|--------|-----------------|----------------------------------------------------------------------------------------|-----|-----|-----|-------------|

| 2nd reference leakage<br>±50 kHz | Lspu4  | 1               | 1st PLL block and 2nd PLL block are<br>simultaneously turned on.<br>RW 1 kHz, VW 1 kHz | —   |     | -40 | dBc         |

| 2nd proximity C / N              | Lspu5  | 1               | 1st PLL block and 2nd PLL block are<br>simultaneously turned on.<br>df = 1 kHz         |     |     | -76 | dBc /<br>Hz |

Note) Unless otherwise specified, V<sub>CC</sub> is 3.0 V and reference signal input level V<sub>REFIN</sub> is 0.6 V[p-p] at f<sub>REFIN</sub> of 19.2 MHz.

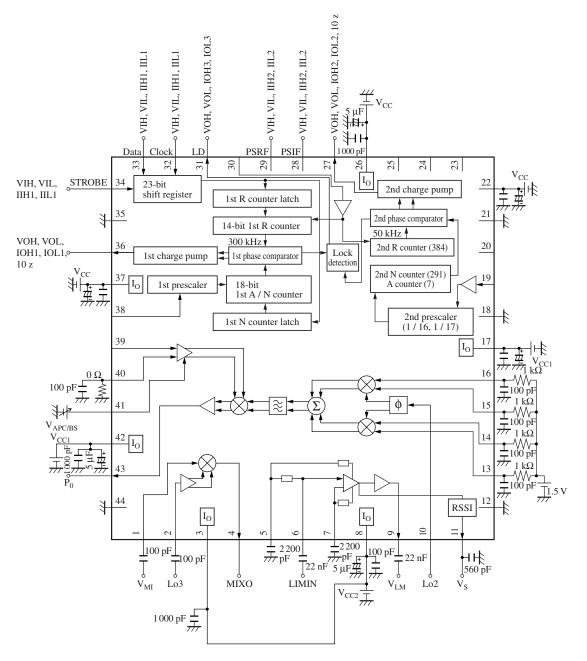

#### 1. Test circuit 1

# Electrical Characteristics at $T_a = 25^{\circ}C$ (continued)

2. Test circuit 2

# Terminal Equivalent Circuits

| Pin No. | Equivalent circuit | Description                                                                                                         | I / O |

|---------|--------------------|---------------------------------------------------------------------------------------------------------------------|-------|

| 1       |                    | RXMIXIN:<br>Reception mixer input pin with an<br>input impedance of approx. 16 kΩ.                                  | Ι     |

| 2       |                    | RXLOIN:<br>Local input pin.                                                                                         | Ι     |

| 3       | _                  | V <sub>CC2</sub> : Mixer power supply pin.                                                                          |       |

| 4       |                    | MXO:<br>Mixer output pin.                                                                                           | 0     |

| 5       |                    | LMDEC1, 2:<br>Coupling pin for limiter amplifier feed-<br>back. Ground this pin through an ex-<br>ternal capacitor. | _     |

| 6       |                    | LMIN:<br>Limiter amplifier input pin with an input impedance of approx. $330 \Omega$ .                              | Ι     |

| 8       |                    | V <sub>CC2</sub> :<br>Pin to provide power supply to the<br>limiter amplifier and RSSI.                             | —     |

| 9       | 9<br>#//           | LMO:<br>Limiter amplifier output pin.                                                                               | 0     |

| Pin No. | Equivalent circuit | Description                                                                                                                                                                                                                                                                                                                                                | I/O |

|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10      |                    | TXLO2:<br>Quadrature modulator local input pin                                                                                                                                                                                                                                                                                                             | Ι   |

| 11      |                    | RSO:<br>RSSI output pin with DC output ac-<br>cording to the input signal level of the<br>limiter amplifier.                                                                                                                                                                                                                                               | 0   |

| 12      | —                  | GNDR: Ground pin.                                                                                                                                                                                                                                                                                                                                          | —   |

| 13      |                    | Q-in:<br>Q signal input pin with the following<br>relationship between the input DC<br>bias and amplitude.DC bias (V)Amplitude V[p-p] $1.5$ $0.5$ (Both phases) $\overline{Q}$ -in:<br>$\overline{Q}$ signal input pin with the following<br>relationship between the input DC<br>bias and amplitude.DC bias (V)Amplitude V[p-p] $1.5$ $0.5$ (Both phases) | I   |

| 15      |                    | I-in:         I signal input pin with the following         relationship between the input DC         bias and amplitude.         DC bias (V)         Amplitude V[p-p]         1.5         0.5 (Both phases)                                                                                                                                               | I   |

| 16      |                    | $\bar{I}$ -in: $\bar{I}$ signal input pin with the followingrelationship between the input DCbias and amplitude.DC bias (V) Amplitude V[p-p]1.50.5 (Both phases)                                                                                                                                                                                           | I   |

| Pin No.  | Equivalent circuit | Description                                                                                                                                                                                                                                                                    | I/O |

|----------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 17       |                    | $V_{CC1}$ :<br>Pin to provide supply voltage to the<br>quadrature modulator. The pin is con-<br>nected to the built-in band gap regu-<br>lator, thus providing stable bias volt-<br>age without being affected by $V_{CC}$ or<br>temperature changes as much as pos-<br>sible. | Ι   |

| 18       | _                  | GNDM:<br>Ground pin for the quadrature modu-<br>lator. Keep the grounding surface wide<br>to lower the impedance.                                                                                                                                                              | _   |

| 19       |                    | 2nd prescaler in:<br>2nd PLL prescaler input pin.                                                                                                                                                                                                                              | Ι   |

| 21       | —                  | GND 2nd CMOS:<br>Ground pin for the 2nd PLL.                                                                                                                                                                                                                                   |     |

| 22       | —                  | V <sub>CC</sub> : Bip power supply pin for the PLL.                                                                                                                                                                                                                            | —   |

| 26       | —                  | V <sub>CC</sub> : 2nd CMOS power supply pin for the PLL.                                                                                                                                                                                                                       | —   |

| 27       |                    | 2nd chargepump out:<br>2nd PLL charge pump output pin.                                                                                                                                                                                                                         | 0   |

| 28<br>29 |                    | 28: 2nd power save in:<br>29: 1st power save in:<br>2nd PLL and 1st PLL power save<br>control input pins.                                                                                                                                                                      | Ι   |

| 30       |                    | Reference in:<br>Reference signal input pin.                                                                                                                                                                                                                                   | I   |

| Pin No.        | Equivalent circuit      | Description                                                                                                                                           | I/O |

|----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 31             |                         | Lock detect out:<br>Lock detection output pin.                                                                                                        | 0   |

| 32<br>33<br>34 | 32<br>33<br>34 <i>m</i> | <ul> <li>32: Clock in:<br/>Clock input pin.</li> <li>33: Serial data in:<br/>Data input pin.</li> <li>34: Strobe in:<br/>Strobe input pin.</li> </ul> | Ι   |

| 35             | —                       | GND 1st / 2nd CMOS:<br>1st and 2nd PLL ground pin.                                                                                                    |     |

| 36             |                         | 1st charge pump out:<br>1st PLL charge pump output pin.                                                                                               | 0   |

| 37             |                         | V <sub>CC</sub> :<br>1st PLL CMOS power supply pin.                                                                                                   | _   |

| 38             |                         | 1st prescaler in:<br>1st PLL prescaler input pin.                                                                                                     | Ι   |

| 39             |                         | TX LO1:<br>Local input pin for the up-mixer. The<br>use of an external balancer is recom-<br>mended to apply balanced input.                          | Ι   |

| 40             |                         | TX LO1R:<br>Local input pin for the up-mixer. The<br>use of an external balancer is recom-<br>mended to apply balanced input.                         | Ι   |

| Pin No. | Equivalent circuit | Description                                                                                                                                                                                                                                                                                       | I / O |

|---------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| 41      | (APC control)      | APC / BS:Pin used for the battery save of the<br>transmission circuit block and the<br>power control of RF output. $V_{APC} (V)$ $V_{APC} (V)$ $O$ to 0.3 $O$ to 0.3 $O$ to $V_{CC}$ $On$ (APC control)The impedance is a minimum of 5 k $\Omega$ .                                               | Ι     |

| 42      |                    | $V_{CC1}$ :<br>Pin to provide power supply to the up-<br>mixer and output amplifier circuit.<br>This pin is connected to the built-in<br>stabilized power supply circuit and<br>provides stable bias voltage without<br>being affected by $V_{CC}$ or temperature<br>changes as much as possible. |       |

| 43      |                    | TXO:<br>RF output pin connected to the output<br>amplifier circuit and has emitter fol-<br>lower output.                                                                                                                                                                                          | 0     |

| 44      |                    | GNDO:<br>Ground pin for the up-mixer and out-<br>put amplifier circuit. This pin is a high-<br>frequency ground pin. Therefore, keep<br>the grounding surface wide to<br>lower the impedance.                                                                                                     |       |

#### Technical Data

#### 1. Serial data interface specifications

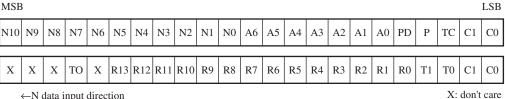

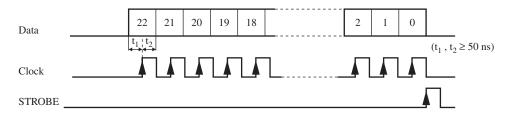

Carrier data is transferred in 23-bit serial data transfer. The serial data is set at the clock falling edge and latched onto the synthesizer at the clock rising edge. It is necessary to input a single STROBE pulse when the 23-bit serial data transfer is completed.

1) Serial interface of 1st synthesizer

1st synthesizer serial data input format

$\leftarrow$ N data input direction

$f_{out} = (P \times N + A) \times f_{in} / R$ Possible set range: 1st A = 0 to 127 or 63, N = 5 to 2047 (N > A)

R = 5 to 16383

#### (1) Control bit

| C0 | C1 |                                           |                                  | Т0 | T1 |

|----|----|-------------------------------------------|----------------------------------|----|----|

| 1  | 0  | 1st synthesizer R counter frequency       | 2nd synthesizer R counter output | 0  | 0  |

|    |    | dividing ratio setting                    | 2nd synthesizer N counter output | 0  | 1  |

| 1  | 1  | 1 1st synthesizer A / N counter frequency | 1st synthesizer R counter output | 1  | 0  |

|    |    | dividing ratio setting                    | 1st synthesizer N counter output | 1  | 1  |

(2) Test contents

#### (3) Data contents

|   | PD<br>Phase comparator<br>polarity selection | P<br>Prescaler frequency<br>dividing ratio | TC<br>Counter test<br>mode setting | TO<br>Output pin test |

|---|----------------------------------------------|--------------------------------------------|------------------------------------|-----------------------|

| 0 | negative                                     | 128 / 129                                  | LD output                          | normal                |

| 1 | positive                                     | 64 / 65                                    | Counter output                     | test                  |

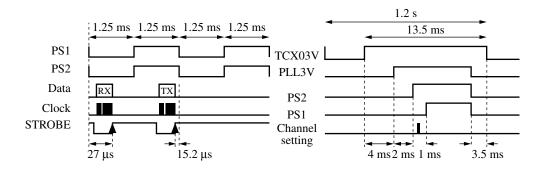

#### 2) Serial transfer timing

Timing chart

X: don't care

#### Technical Data (continued)

2. 2nd synthesizer frequency dividing ratio

Set frequency (frequency dividing ratio)  $f_{out2} = 233.15$  MHz,  $f_r = 50$  kHz, (P = 16, N = 291, A = 7, R = 384 fixed) Reference frequency  $f_{REFIN} = 19.2$  MHz

| MS | SB  |    |    |    |    |    |    |    |    |    |    |   |   |   |    |    |    |    |    |   | LSB |

|----|-----|----|----|----|----|----|----|----|----|----|----|---|---|---|----|----|----|----|----|---|-----|

| N1 | 0 1 | N9 | N8 | N7 | N6 | N5 | N4 | N3 | N2 | N1 | N0 | Х | Х | Х | A3 | A2 | A1 | A0 | PD | Р | Х   |

| 0  |     | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 0 | 0 | 0 | 0  | 1  | 1  | 1  | 1  | 0 | 0   |

|    |     |    |    |    |    |    |    |    |    |    |    |   |   |   |    |    |    |    |    |   |     |

| X | Х | Х | Х | Х | R13 | R12 | R11 | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 | R0 | Х | Х |

|---|---|---|---|---|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---|---|

| 0 | 0 | 0 | 0 | 0 | 0   | 0   | 0   | 0   | 0  | 1  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 |

#### 3. Unlock detection and LD output specifications

- 1) The AND of the LD signal (2) of the 1st synthesizer block and the LD signal (3) of the 2nd synthesizer block is output.

- 2) 1st synthesizer block

When the synthesizer block is locked, the LD output level will be high. When the synthesizer block is unlocked, the LD output level will be low. The detection time is  $3.3 \,\mu$ s. As for the precision of detection, unlock output turns on if the devided frequency output of the circuit is ( $52 \times 4$ ) ns slower or faster than it should be at the frequency free for 300 kHz. The lock signal is output in power save mode.

#### 3) 2nd synthesizer block

When the synthesizer block is locked, the LD output level will be high. When the synthesizer block is unlocked, the LD output level will be low. The detection time is 20  $\mu$ s. As for the precision of detection, unlock output turns on if the devided frequency output of the circuit is (52 × 4) ns slower or faster than it should be at the frequency f<sub>ref</sub> of 50 kHz. The lock signal is output in power save mode.

| 1st synthesizer         | 2nd synthesizer         | LD output |  |  |

|-------------------------|-------------------------|-----------|--|--|

| Lock or power save mode | Lock or power save mode | High      |  |  |

| Unlock                  | Lock or power save mode | Low       |  |  |

| Lock or power save mode | Unlock                  | Low       |  |  |

| Unlock                  | Unlock                  | Low       |  |  |

#### 4. Other specifications

- 1) Clock, Data, and STROBE all are high-active logics.

- 2) When the IC is turned on, set the IC to power save mode by setting both PS1 and PS2 to low-level. After serial data is input, set the IC to operating mode by setting both PS1 and PS2 to high-level.

#### Technical Data (continued)

3. TX-RX burst / intermittent reception lockup time

Unless otherwise specified,  $V_{CC}$  = 3.0 V, and  $f_{REF}$  = 19.2 MHz. The lockup time means converging time into ±1 kHz.

1) Test circuit

- 2) Serial control timing

- (1) At TX-RX burst

(2) At intermittent reception

# Technical Data (continued)

4. Oscillator frequency by channel ( $f_{RFIN}$ )

| ch  | f <sub>RFIN</sub> <tx> (MHz)</tx> | f <sub>RFIN</sub> <rx> (MHz)</rx> | ch | f <sub>RFIN</sub> <tx> (MHz)</tx> | $f_{RFIN} < RX > (MHz)$ |

|-----|-----------------------------------|-----------------------------------|----|-----------------------------------|-------------------------|

| 251 | 1 660.5                           | 1 649.7                           | 31 | 1671.0                            | 1660.2                  |

| 252 | 1 660.8                           | 1650.0                            | 32 | 1671.3                            | 1660.5                  |

| 253 | 1 666.1                           | 1 650.3                           | 33 | 1671.6                            | 1 660.8                 |

| 254 | 1 666.4                           | 1 650.6                           | 34 | 1671.9                            | 1661.1                  |

| 255 | 1 666.7                           | 1 650.9                           | 35 | 1 672.2                           | 1661.4                  |

| 1   | 1 662.0                           | 1651.2                            | 36 | 1 672.5                           | 1661.7                  |

| 2   | 1 662.3                           | 1651.5                            | 37 | 1 672.8                           | 1662.0                  |

| 3   | 1 662.6                           | 1651.8                            | 38 | 1 673.1                           | 1662.3                  |

| 4   | 1 662.9                           | 1652.1                            | 39 | 1 673.4                           | 1662.6                  |

| 5   | 1 663.2                           | 1652.4                            | 40 | 1 673.7                           | 1662.9                  |

| 6   | 1 663.5                           | 1652.7                            | 41 | 1 674.0                           | 1663.2                  |

| 7   | 1 663.8                           | 1653.0                            | 42 | 1 674.3                           | 1 663.5                 |

| 8   | 1 664.1                           | 1653.3                            | 43 | 1 674.6                           | 1 663.8                 |

| 9   | 1 664.4                           | 1653.6                            | 44 | 1 674.9                           | 1664.1                  |

| 10  | 1 664.7                           | 1653.9                            | 45 | 1675.2                            | 1664.4                  |

| 11  | 1 665.0                           | 1654.2                            | 46 | 1 675.5                           | 1 664.7                 |

| 12  | 1 665.3                           | 1654.5                            | 47 | 1 675.8                           | 1665.0                  |

| 13  | 1 665.6                           | 1654.8                            | 48 | 1 676.1                           | 1665.3                  |

| 14  | 1 665.9                           | 1655.1                            | 49 | 1 676.4                           | 1665.6                  |

| 15  | 1 666.2                           | 1655.4                            | 50 | 1 676.7                           | 1665.9                  |

| 16  | 1 666.5                           | 1655.7                            | 51 | 1 677.0                           | 1666.2                  |

| 17  | 1 666.8                           | 1656.0                            | 52 | 1 677.3                           | 1 666.5                 |

| 18  | 1 667.1                           | 1656.3                            | 53 | 1 677.6                           | 1 666.8                 |

| 19  | 1 667.4                           | 1656.6                            | 54 | 1 677.9                           | 1667.1                  |

| 20  | 1 667.7                           | 1656.9                            | 55 | 1 678.2                           | 1667.4                  |

| 21  | 1 668.0                           | 1657.2                            | 56 | 1 678.5                           | 1667.7                  |

| 22  | 1 668.3                           | 1657.5                            | 57 | 1 678.8                           | 1 668.0                 |

| 23  | 1 668.6                           | 1657.8                            | 58 | 1 679.1                           | 1668.3                  |

| 24  | 1 668.9                           | 1658.1                            | 59 | 1 679.4                           | 1 668.6                 |

| 25  | 1 669.2                           | 1658.4                            | 60 | 1 679.7                           | 1 668.9                 |

| 26  | 1 669.5                           | 1658.7                            | 61 | 1 680.0                           | 1 669.2                 |

| 27  | 1 669.8                           | 1659.0                            | 62 | 1 680.3                           | 1 669.5                 |

| 28  | 1 670.1                           | 1659.3                            | 63 | 1 680.6                           | 1 669.8                 |

| 29  | 1 670.4                           | 1659.6                            | 64 | 1 680.9                           | 1670.1                  |

| 30  | 1 670.7                           | 1659.9                            | 65 | 1681.2                            | 1 670.4                 |

# Technical Data (continued)

| 4. | Oscillator | frequency | by | channel | (f <sub>RFIN</sub> ) | (continued) |

|----|------------|-----------|----|---------|----------------------|-------------|

|----|------------|-----------|----|---------|----------------------|-------------|

| ch | f <sub>RFIN</sub> <tx> (MHz)</tx> | f <sub>RFIN</sub> <rx> (MHz)</rx> | ch      | f <sub>RFIN</sub> <tx> (MHz)</tx> | f <sub>RFIN</sub> <rx> (MHz)</rx> |

|----|-----------------------------------|-----------------------------------|---------|-----------------------------------|-----------------------------------|

| 66 | 1681.5                            | 1670.7                            | 77      | 1 684.8                           | 1674.0                            |

| 67 | 1 681.8                           | 1671.0                            | 78      | 1685.1                            | 1674.3                            |

| 68 | 1 682.1                           | 1671.3                            | 79      | 1 685.4                           | 1674.6                            |

| 69 | 1 682.4                           | 1671.6                            | 80      | 1 685.7                           | 1674.9                            |

| 70 | 1 682.7                           | 1671.9                            | 81      | 1 686.0                           | 1675.2                            |

| 71 | 1 683.0                           | 1672.2                            | 82      | 1 686.3                           | 1675.5                            |

| 72 | 1 683.3                           | 1672.5                            | max.    | 1 686.3                           | 1 649.7                           |

| 73 | 1 683.6                           | 1 672.8                           |         | (1st)                             | (2nd)                             |

| 74 | 1 683.9                           | 1673.1                            | Inter-  | 1662.6                            | 233.15                            |

| 75 | 1 684.2                           | 1 673.4                           | mittent |                                   |                                   |

| 76 | 1 684.5                           | 1 673.7                           |         |                                   |                                   |

5.  $P_D - T_a$  curves of QFN044-P-0606A

#### Technical Data (continued) 6. Main characteristics APC control voltage characteristics Wideband spurious characteristics Transmission output level (dBm)/ adjacent channel leakage suppression (dBc)/ $8 \times Lo$ (dBc) 0 0 20 -10 -1018 -20 -20 16 Transmission output (%) -30 -30 14 Spurious (dBm) Modulation accuracy -40 -40 12 Adjacent channel at 300 kHz -50 10 -50 $8 \times Lo$ -60 Adjacent channel at 600 kHz 8 -60-70 -70 6 Modulation accuracy -80 4 -80RLV: 0.0 dBm Lo1:1672.5 MHz, -10 dBm Lo2: 233.15 MHz, -10 dBm 2 AT 15 dB RB 1 MHz -90 -90 I / Q signal DC bias: 1.5 V, amplitude: 500 mV[p-p], ST 200 ms VB 1MHz -100 PN9-level continuous wave -1000 60k 600k 6M 60M 600M 6G 6 60 600 6k $0 \ \ 0.2 \ 0.4 \ 0.6 \ 0.8 \ \ 1 \ \ 1.2 \ 1.4 \ 1.6 \ 1.8 \ \ 2 \ \ 2.2 \ \ 2.4 \ 2.6 \ \ 2.8 \ \ 3$ 0.6 (Hz) APC control voltage (V) AN6591FJM Mix.I / O characteristics AN6591FJM Lim. characteristics 120 120 60°C 110 110 100 100 90 90 Lim. output level (dBµ) Mix. output level (dBµ) 20°C 80 80 -20% 70 70 60 60 60 50 50 40 40 30 30 20 20 10 10 0 0 0 10 20 30 40 50 60 70 80 90 100 110 120 0 10 20 30 40 50 60 70 80 90 100 110 120 Limiter input level (dBµ) Mix. input level (dBµ)

Note) 1. Unless otherwise specified, the test conditions conform to electrical characteristics. 2. The values in the above are reference values for designing and not guaranteed.

8 6

4 2 0 ۱ NF

-20 -18

-16 -14 -12 -10 -8

Local input level (dBm)

### Technical Data (continued)

Note) 1. Unless otherwise specified, the test conditions conform to electrical characteristics. 2. The values in the above are reference values for designing and not guaranteed.

-2

0

-6 -4

# Request for your special attention and precautions in using the technical information and semiconductors described in this material

- (1) An export permit needs to be obtained from the competent authorities of the Japanese Government if any of the products or technologies described in this material and controlled under the "Foreign Exchange and Foreign Trade Law" is to be exported or taken out of Japan.

- (2) The technical information described in this material is limited to showing representative characteristics and applied circuits examples of the products. It neither warrants non-infringement of intellectual property right or any other rights owned by our company or a third party, nor grants any license.

- (3) We are not liable for the infringement of rights owned by a third party arising out of the use of the product or technologies as described in this material.

- (4) The products described in this material are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (5) The products and product specifications described in this material are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (6) When designing your equipment, comply with the guaranteed values, in particular those of maximum rating, the range of operating power supply voltage, and heat radiation characteristics. Otherwise, we will not be liable for any defect which may arise later in your equipment. Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (7) When using products for which damp-proof packing is required, observe the conditions (including shelf life and amount of time let standing of unsealed items) agreed upon when specification sheets are individually exchanged.

- (8) This material may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.